Инвестиции

Стартапам

Инвесторам

Инвесторам

Аналитика

Инвестиции

Стартапам

Инвесторам

Аналитика

Спрос и кооперация

Спрос и кооперация

Развитие и продвижение бизнеса

Спрос

Кооперация

Спрос и кооперация

Развитие и продвижение бизнеса

Спрос

Кооперация

Гранты и кредиты

Гранты и кредиты

Инфраструктура

Инфраструктура

Современные пространства

для бизнеса

для бизнеса

Инфраструктура

Современные пространства

для бизнеса

для бизнеса

Патентование

Патентование

Обучение и карьера

Обучение и карьера

Проекты для мегаполиса

Проекты для мегаполиса

Технологические городские проекты

Проекты для мегаполиса

О Кластере

О Кластере

Лидеры цифровой трансформации

Лидеры цифровой трансформации

Академия инноваторов

Академия инноваторов

Новатор Москвы

Новатор Москвы

Обучение и карьера

Обучение и карьера

Образовательные программы и база знаний

Обучение

Обучение и карьера

Образовательные программы и база знаний

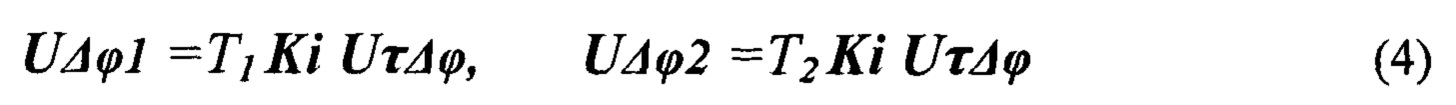

интервалов счета; 6 - группа n входных счетчиков импульсов, измеряющих целую часть частоты ƒ входного сигнала; 7 - многовходовая схема "И-НЕ", формирующая импульс сброса в последний такт счета интервала

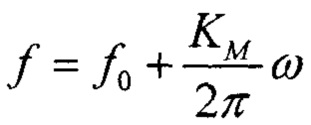

интервалов счета; 6 - группа n входных счетчиков импульсов, измеряющих целую часть частоты ƒ входного сигнала; 7 - многовходовая схема "И-НЕ", формирующая импульс сброса в последний такт счета интервала  , где KM - коэффициент передачи гироскопа - магнетрона, ω - измеряемая угловая скорость подвижного объекта (ПО). Иначе формула записывается в виде ƒ=ƒ0+Δƒ,

, где KM - коэффициент передачи гироскопа - магнетрона, ω - измеряемая угловая скорость подвижного объекта (ПО). Иначе формула записывается в виде ƒ=ƒ0+Δƒ,  . При этом частота эталонная ƒ0 может лежать в интервале частот (0.1-10), ГГц.

. При этом частота эталонная ƒ0 может лежать в интервале частот (0.1-10), ГГц. и периоды следования импульсов измерительного интервала

и периоды следования импульсов измерительного интервала  . С помощью триггера 8, схемы 4 и блока логики 10 измерительный интервал в отрезки времени ΔT заполняется счетными импульсами UcΔϕ. Данное решение поясняется графиками сигналов фиг. 4 и формулами (алгоритмами). Помимо заданных частот ƒ0 и ƒ, на фиг. 4 приведен и график сигнала счетной частоты ƒс, при этом для примера

. С помощью триггера 8, схемы 4 и блока логики 10 измерительный интервал в отрезки времени ΔT заполняется счетными импульсами UcΔϕ. Данное решение поясняется графиками сигналов фиг. 4 и формулами (алгоритмами). Помимо заданных частот ƒ0 и ƒ, на фиг. 4 приведен и график сигнала счетной частоты ƒс, при этом для примера

формируется одним счетчиком 5 от опорной частоты ƒ0 естественным путем по сигналу переполнения, который передним фронтом переписывает данные со счетчика 6 входной частоты ƒ в регистр 11, а по заднему фронту переводит группу счетчиков к начальному нулевому состоянию. Использование регистра позволяет избежать «мигания» выходного кода для целой части частоты ƒ, позволяет обращаться к этой информации непрерывно, что является достоинством для использования устройства в качестве датчика, и сильно упрощает коррекцию для дробной части в устройстве 15, которое может быть здесь реализовано на ПЛИСе вместо микроконтроллера, как в аналоге.

формируется одним счетчиком 5 от опорной частоты ƒ0 естественным путем по сигналу переполнения, который передним фронтом переписывает данные со счетчика 6 входной частоты ƒ в регистр 11, а по заднему фронту переводит группу счетчиков к начальному нулевому состоянию. Использование регистра позволяет избежать «мигания» выходного кода для целой части частоты ƒ, позволяет обращаться к этой информации непрерывно, что является достоинством для использования устройства в качестве датчика, и сильно упрощает коррекцию для дробной части в устройстве 15, которое может быть здесь реализовано на ПЛИСе вместо микроконтроллера, как в аналоге.

и должен содержать необходимое число каскадов n.

и должен содержать необходимое число каскадов n. , накопленная фаза для разностной частоты Δƒ, которая с каждым интервалом изменяется на величину

, накопленная фаза для разностной частоты Δƒ, которая с каждым интервалом изменяется на величину  , пропорциональную разностной частоте ƒ-ƒ0. Поскольку в нашем случае Δƒ>0, избыток накопленной фазы будет с каждым интервалом уменьшаться.

, пропорциональную разностной частоте ƒ-ƒ0. Поскольку в нашем случае Δƒ>0, избыток накопленной фазы будет с каждым интервалом уменьшаться. . После этого цикл может повторяться до бесконечности.

. После этого цикл может повторяться до бесконечности.